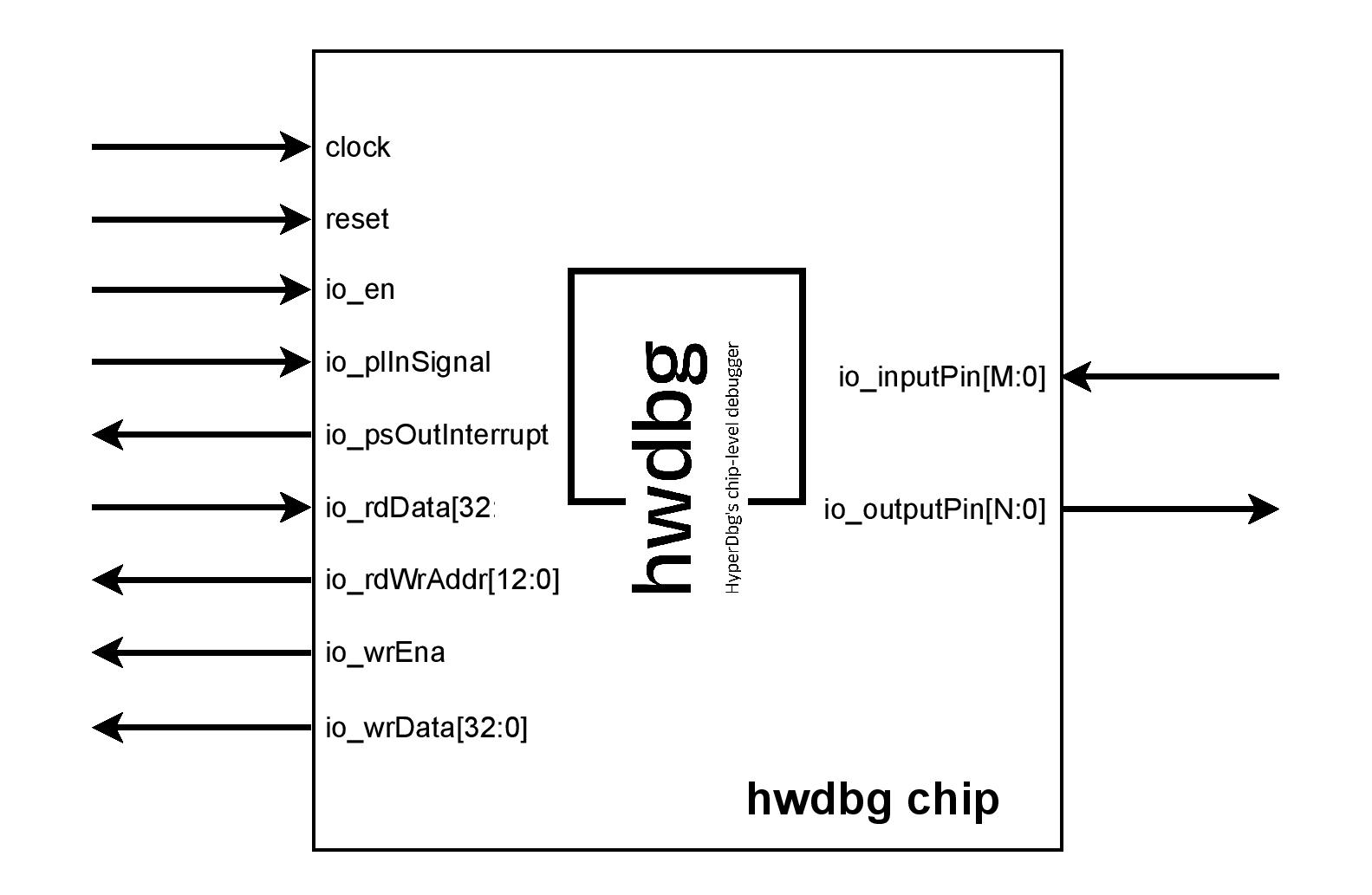

Debugging Input/Output Pins

There are five divisions of pins in hwdbg.

- Chip pins: Contains the clock signal [clock], reset [reset], and chip enable [io_en] all as inputs

- Interrupt lines: Contains [io_plInSignal] as PS to PL signal input, and [io_psOutInterrupt] as PL to PS interrupt output

- BRAM ports: Contains [io_rdData] as read data input, [io_rdWrAddr] as read/write address output, [io_wrEna] as enable writing, and [io_wrData] as write data all as output

- Input pins: Contains [io_inputPin0...n] as input pins

- Output pins: Contains [io_outputPin0..n] as output pins

These pins are also illustrated in figure below.

| Division | Pin | Description |

|---|---|---|

| Chip Pins | clock, reset, io_en | Clock signal (input), Reset signal (input), Chip enable signal (input) |

| Interrupt Lines | io_plInSignal, io_psOutInterrupt | PS to PL signal (input), PL to PS interrupt (output) |

| BRAM Ports | io_rdData, io_rdWrAddr, io_wrEna, io_wrData | Read data (input), Read/write address (output), Enable writing (output), Write data (output) |

| Input Pins | io_inputPin0...n (customizable) | Input pins (input) |

| Output Pins | io_outputPin0...n (customizable) | Output pins (output) |