Interpreting Module

Once valid data is received from either the PS, the interpreting module takes charge of analyzing the incoming packets. It decodes the received data, interprets its meaning or purpose, and triggers any necessary actions or responses within the hwdbg. This module involves parsing incoming commands, executing debugging operations, or generating responses to be sent back to the PS.

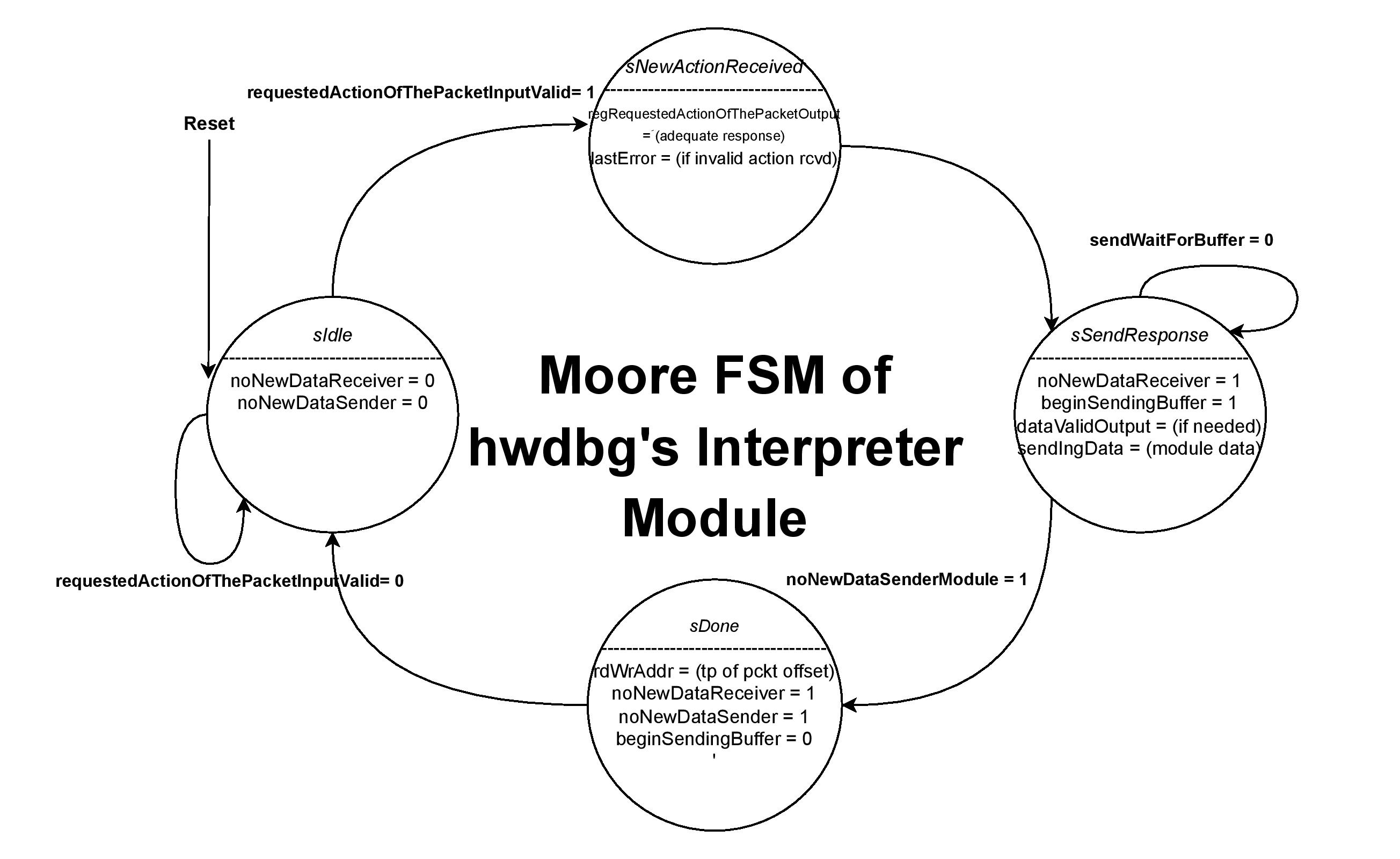

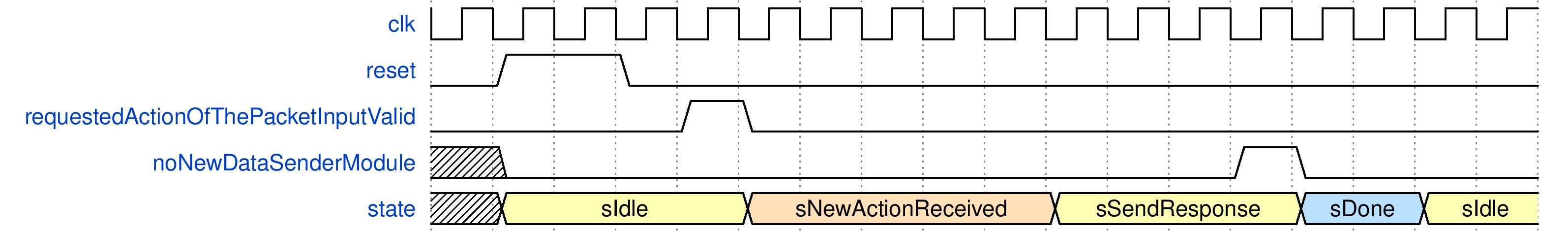

This module is designed to process incoming data packets and generate appropriate responses based on the actions requested by these packets. Initially, the FSM is in the sIdle state, where it remains until a valid packet input is received from the receiver module (requestedActionOfThePacketInputValid = 1). In this state, no new data is being received or sent by the interpreter (noNewDataReceiver = 0, noNewDataSender = 0).

Upon detecting a valid packet input, the FSM transitions to the receiving (sNewActionReceived) state. Here, the module interprets the requested action and prepares the response (requestedActionOfThePacketOutput = adequate response). If the action is invalid, an error flag (lastError = if invalid action received) is set. After processing the action, the FSM moves to the sSendResponse state, where it prepares to send the response data. In this state, the module sets signals indicating it is ready to send data (noNewDataReceiver = 1, beginSendingBuffer = 1) and the data to be sent is made available (sendingData = module data). If further synchronization is required, the FSM ensures that the data is valid and waits for the buffer to be ready (sendWaitForBuffer = 0).

Once the response data has been sent, the current FSM transitions to the sDone state, where it updates the read/write address (rdWrAddr = type of packet offset) and signals that the receiving and sending processes are complete (noNewDataReceiver = 1, noNewDataSender = 1). Finally, the FSM returns to the sIdle state, ready to process the next incoming packet.